#USB 3.2 Retimer

Explore tagged Tumblr posts

Photo

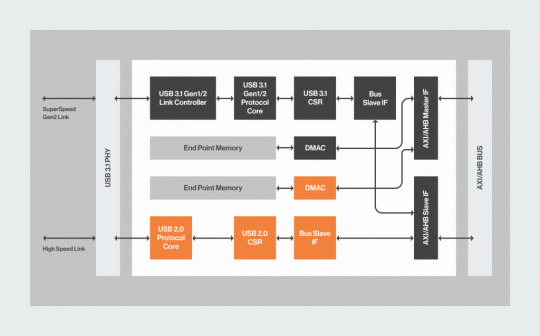

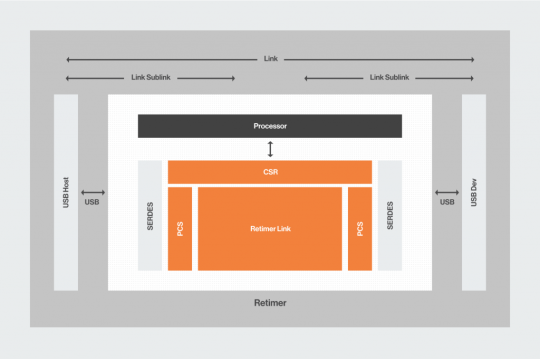

USB 3.1 Appendix E standard-USB 3.2 Retimer

We offer USB IP subsystem, FPGA boards, SERDES interface, USB 3.1 Device Controller, USB 3.2 Retimer, SRIS architecture, MCU CSR interface.

#USB 3.1 Appendix E standard#usb 3.2 retimer#usb ip subsystem#fpga boards#serdes interface#mcu csr interface

0 notes

Text

Parade Introduces USB Type-C Retimers for Peripheral Devices Supporting USB 3.2 Gen 2 and DisplayPort 1.4a HBR3 with Internal Signal Muxing

Parade Introduces USB Type-C Retimers for Peripheral Devices Supporting USB 3.2 Gen 2 and DisplayPort 1.4a HBR3 with Internal Signal Muxing

By regenerating the received and transmitted signals to the USB Type-C receptacle, repeaters for USB Type-C peripherals offer increased system design flexibility and signal compliance margin

SAN JOSE, Calif.–(BUSINESS WIRE)–Parade Technologies, Ltd. (Taiwan OTC: 4966.TWO), a leading high-speed interface, video display, and touch controller IC supplier, today announced the PS8822, a USB Type-C…

View On WordPress

0 notes

Text

Die-to-Die Interposer I/O-USB 3.1 Device Controller-USB 3.2 Retimer

Interposers for bundling of ULK and 3D-ICs need to help huge quantities of Die-to-Die Interposer with I/O pitch under 50 μm. The proceeding progression of semiconductor gadgets consistently expands the quantity of worldwide interconnects and higher I/O counts in this manner driving more the significance of more modest component size interconnects. Quite possibly the most troublesome specialized challenge for interconnects includes new material turn of events, nonetheless, it is accepted that moderation of the effect of size scaling like its viewpoint proportion (thickness/width) and dividing could fill the hole for high thick bundling necessity brought by Moore's Law. The cutting edge substrate configuration rules require a cycle capacity with under a 50um pitch to oblige driving edge portable applications like Wide I/O memory-Logic bundling coordination. Current natural substrates are restricted by CTE jumble, wiring thickness, and poorly layered soundness.

Wafer-based silicon interposers can accomplish high I/Os at a fine pitch yet are restricted by the significant expense. Glass is an ideal interposer material because of its protecting property, huge board accessibility, and CTE match to silicon. The primary focal point of this work is on a) electrical and mechanical plan, b) TPV and barely recognizable difference arrangement, and c) joining process and electrical portrayal of flimsy glass interposers. This work interestingly shows a high throughput arrangement of 30 μm contribute TPVs ultrathin glass utilizing an equal laser process. A combination interaction was shown for glass interposer with polymer develop layers on the two sides.

USB 3.1 Device Controller-USB 3.2 Retimer Battery-powered batteries are the excellent wellspring of energy for PEDs and a key to their ideal presentation security. With the amazing advancement in battery charging innovations and USB principles, multifunctional PEDs have continually had the option to meet the solicitations of our everyday existence helpfully. In any case, these PEDs charge their battery-powered batteries at various voltage and power levels in this way each requires an alternate sort of battery charger. In this paper idea of a widespread USB charger has been investigated i.e a solitary USB charger for all the PEDs. To understand this all-inclusive USB charger initial, a complete outline of USB guidelines and particulars has been illustrated.

The glass interposer had stable electrical properties up to 20GHz and a low addition loss of under 0.15dB was estimated for TPVs at 9GHz. 3D IC bundles with stacked silicon interconnect (SSI) have numerous presentation benefits over traditional flip-chip bundles. Utilizing SSI, different bite the dust utilizing something similar or different innovation can be associated with one another with the utilization of an interposer. The interposer permits an enormous number of biting the dust to kick the bucket associations, empowering higher interconnect transfer speed, lower power utilization, and lower I/O inertness. With the interest for higher joining, extra-enormous interposer bundles were created with bite the dust sizes more prominent than the reticle size.

Our review assessed the board level dependability of 55 mm 3D IC bundles with interposers as extensive as 45 mm. The bundles were collected with different 20 nm Cu/ELK (outrageous low-k) bite the dust mounted on through-silicon using (TSV) interposers. With incredibly huge interposer bundles, the get-together interaction and materials should be streamlined to diminish the bundle pressure and warpage that can prompt bundle or bind joint disappointments. The impact of various factors, for example, board cushion plan and get-together ready level dependability were assessed on 55 mm 3D IC bundles with a very enormous TSV interposer gathered with natural substrates. Cover development (1-piece versus 2-piece cover) and substrate material properties that can influence bundle warpage and weld joint dependability were additionally evaluated.

The following GaN-based dynamic cinch flyback converter has been examined alongside some conceivable designs for single-port and multi-port all-inclusive chargers. USB-based assaults have expanded in intricacy lately. Present-day goes after now join a wide scope of assault vectors, from social designing to flag infusion. To address these difficulties, the security local area has answered with a developing arrangement of divided guards. In this work, we overview and sort USB assaults and safeguards, binding together perceptions from both companions evaluated exploration and industry. Our systematization extricates hostile and protective natives that work across layers of correspondence inside the USB environment. In light of our scientific categorization, we find that USB goes after regularly misuse the trust-as a matter of course nature of the biological system, and rise above various layers inside a product stack; none of the current protections give a total arrangement, and arrangements it is best to extend different layers.

We then, at that point, foster the principal formal confirmation of the as of late delivered USB Type-C Authentication detail and uncover crucial imperfections in the determination's plan. Individualized computing with reasonable PCs and their fringe gadgets turns out to be more well known. To utilize such gadgets all the more effectively and work at their convenience, individuals need to divide encompassing fringe gadgets among PCs with next to no chance of their registering surroundings. The new gadget sharing advancements in the unavoidable registering region are not adequate for the fringe gadgets of PCs because these advances don't give the organization straightforwardness to applications and gadget drivers. In this paper, we propose USB/IP as a straightforward gadget sharing component over IP organizations.

0 notes

Video

tumblr

USB 3.1 Device Controller-USB 3.2 Retimer

We offer USB IP subsystem, FPGA boards, SERDES interface, USB 3.1 Device Controller, USB 3.2 Retimer, SRIS architecture, MCU CSR interface.

0 notes

Text

MCU CSR interface-USB IP subsystem

The USB interface is the development port on the motherboard for associating different outer gadgets. These development interfaces can be printers, outer Modem, scanners, streak drives, MP3 players, CDs, DV, portable plates, cell phones, tablets, We offer USB IP subsystem, FPGA boards, SERDES interface, USB 3.1 Device Controller, USB 3.2 Retimer, SRIS architecture, MCU CSR interface and other outside gadgets associated with your PC. In addition, broadening the interface additionally empowers the interconnection between PCs.

SB is the truncation for Universal Serial Bus. However, as of not long ago, it was broadly applied. Augmentation to the current PC interfaces. The current board is predominantly utilized USB1.1 and USB2.0, the USB variant of the similarity between the well.

Open Five is a solution-centric silicon company that is uniquely positioned to design processor agnostic SoC architecture. With customizable and differentiated IP, Open Five develops domain-specific SoC architecture based on high-performance, highly-efficient, cost-optimized IP to deliver scalable, USB IP subsystem optimized, differentiated silicon. Open Five offers end-to-end expertise in Architecture, Design Implementation, Software, Silicon Validation and Manufacturing to deliver high-quality silicon.

This is the thing that makes the marks of the Object techniques accessible to the compiler and the code assembles with next to no blunder. Recollect whether the interface attempts to proclaim a public case technique announced 'last' in the Object class then, at that point, it'll result in an incorporate time blunder.

For instance, 'public last Class get Class ()' is a public case technique announced 'last' in the Object class, and consequently on the off chance that an interface attempts to proclaim a strategy with this signature, the aggregation will fizzle.

The current load up is by and large used to help USB work control chipsets, motherboards are likewise furnished with USB interface attachment, and notwithstanding the backplane connector, the load up additionally put away a USB pin, you can associate the suspension front As a USB interface for simple use (note that the wiring to the motherboard manual painstakingly read the guide and press associate, don't pick some unacceptable leaving gear harm).

What's more, the USB interface can likewise be associated using an exceptional USB link to accomplish twofold machine interconnection, and more can be extended through the Hub interface.

With a transmission speed USB (USB1.1 is 12Mbps, USB2.0 is 480Mbps), simple to utilize, hot-swappable, associate the adaptable, autonomous power supply, and so on, can interface a mouse, console, In any case, how are we ready to assemble code having Object strategy approaches the references of an interface type in Java? We as a whole realize that the object of the executing class (and henceforth its sort) will be allocated to just at run time and we can arrange a code provided that the compiler tracks down a strategy for that mark in the proclaimed kind (either announced straightforwardly or acquired from super classes).

This is right for classes in Java, yet just too some degree right for interfaces in Java. Astonished? How about we attempt to get what inside occurs on account of interfaces.

0 notes

Photo

We offer USB IP subsystem, FPGA boards, SERDES interface, USB 3.1 Device Controller, USB 3.2 Retimer, SRIS architecture, MCU CSR interface.

0 notes

Photo

We offer USB IP subsystem, FPGA boards, SERDES interface, USB 3.1 Device Controller, USB 3.2 Retimer, SRIS architecture, MCU CSR interface.

0 notes